# CMS8S589x series Reference Manual

Enhanced flash memory 8-bit 1T 8051 microcontroller Rev. 1.05

Please be reminded about following CMS's policies on intellectual property

<sup>\*</sup> Cmsemicron Limited(denoted as 'our company' for later use) has already applied for relative patents and entitled legal rights. Any patents related to CMS's MCU or other producrts is not authorized to use. Any individual, organization or company which infringes s our company's interlectual property rights will be forbidden and stopped by our company through any legal actions, and our company will claim the lost and required for compensation of any damage to the company.

<sup>\*</sup> The name of Cmsemicron Limited and logo are both trademarks of our company.

<sup>\*</sup> Our company preserve the rights to further elaborate on the improvements about products' function, reliability and design in this manual. However, our company is not responsible for any usage about this munal. The applications and their purposes in this manual are just for clarification, our company does not guarantee that these applications are feasible without further improvements and changes, and our company does not recommend any usage of the products in areas where people's safety is endangered during accident. Our company's products are not authorzed to be used for life-saving or life support devices and systems.our company has the right to change or improve the product without any notification, for latest news, please visit our website: www.mcu.com.cn

# **Table of content**

| CMS8       | S589x series                            |           |

|------------|-----------------------------------------|-----------|

| 1. Ce      | entral processing unit (CPU)            | 11        |

| 1.1        | Reset vector (0000H)                    | 11        |

| 1.2        | BOOT Partition                          |           |

| 1.3        | Accumulator (ACC)                       |           |

| 1.4        | B register (B)                          |           |

|            |                                         |           |

| 1.5        | Stack pointer register (SP)             |           |

| 1.6        | Data pointer register (DPTR0/DPTR1)     |           |

| 1.7        | Data pointer selection register (DPS)   |           |

| 1.8        | Program status register (PSW)           |           |

| 1.9        | Program counter (PC)                    |           |

| 1.10       | Timing access register (TA)             |           |

| 2. Me      | emory and register map                  |           |

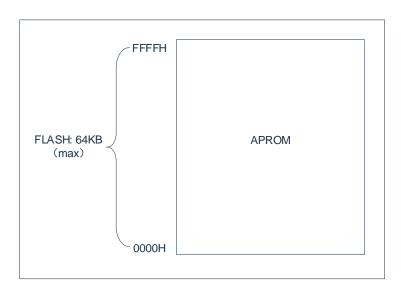

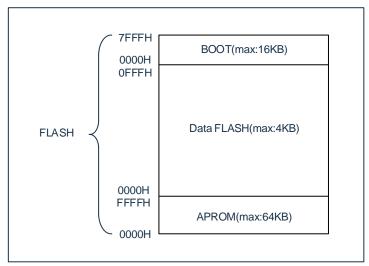

| 2.1        | Program memory APROM                    |           |

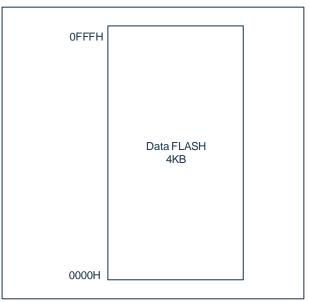

| 2.2        | Non-volatile data storage Data FLASH    | 18        |

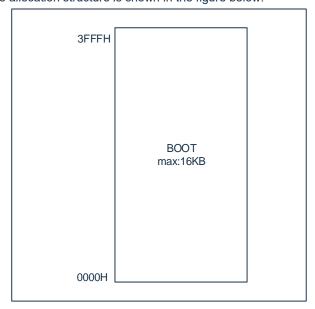

| 2.3        | Program memory BOOT                     | 18        |

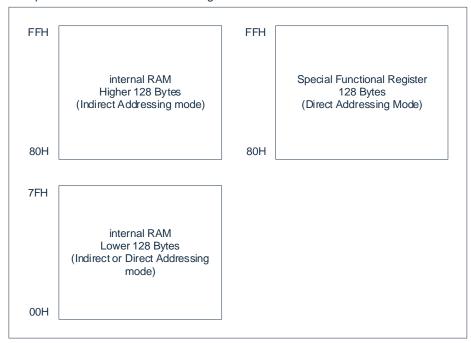

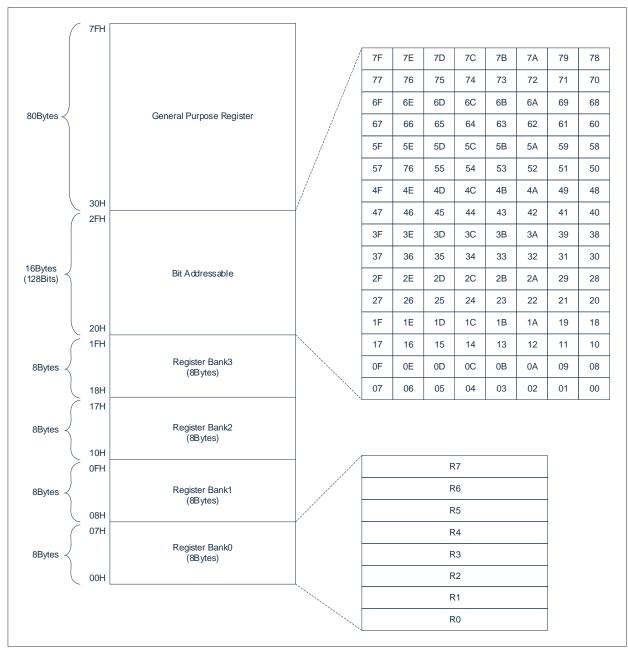

| 2.4        | General data memory RAM                 |           |

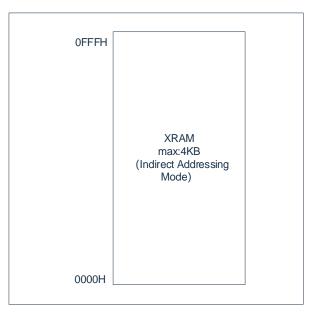

| 2.5        | General external data register XRAM     |           |

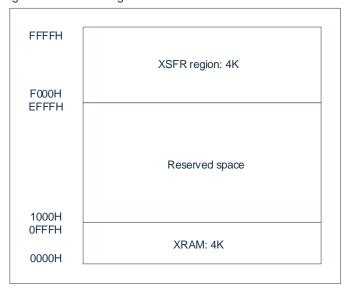

| 2.6        | Special function register SFR           |           |

| 2.7        | External special function register XSFR |           |

|            | eset                                    |           |

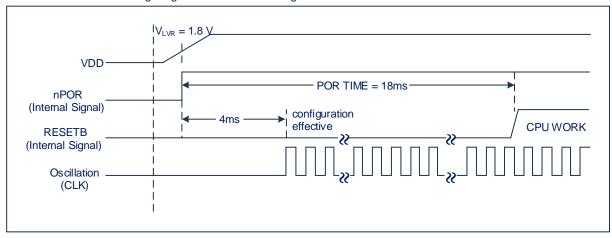

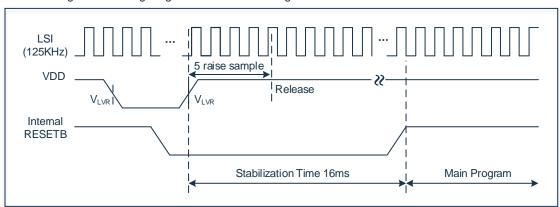

| 3.1        | Power-on reset                          |           |

| 3.2        | External Reset.                         |           |

| 3.3<br>3.4 | LVR Low voltage reset                   |           |

| 3.5        | Window Watchdog Reset                   |           |

| 3.6        | Software Reset                          |           |

| 3.7        | CONFIG state protection reset           |           |

| 3.8        | Power-on configuration monitoring reset |           |

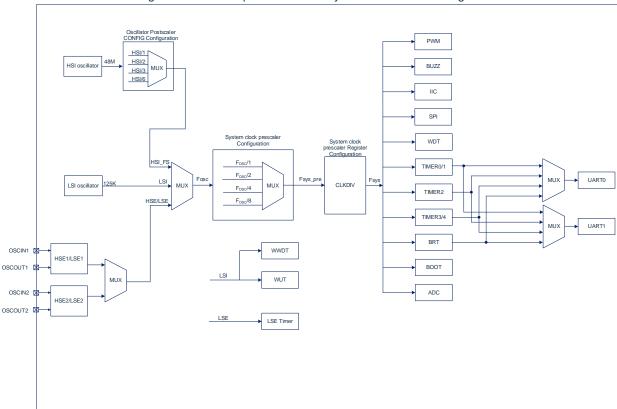

| 4. CI      | ock Structure                           | 35        |

| 4.1        | System Clock Structure                  |           |

| 4.2        | Related Registers                       |           |

| 4.2        | 2.1 Oscillator Control register CLKDIV  | 36        |

| 4.2        | v                                       |           |

| 5. Po      | ower management                         |           |

| 5.1        | Power Management register PCON          |           |

| 5.2        | Power Monitoring register LVDCON        |           |

| 5.3        | IDLE idle mode                          |           |

| 5.4        | STOP sleep mode                         |           |

| 5.4<br>5.4 | •                                       |           |

| 5.4<br>5.4 | ·                                       |           |

| 5.4        | ·                                       |           |

| 5.4        | ·                                       |           |

|            | .mcu.com.cn 3 / 224                     | Rev. 1.05 |

|    | 5.4.6  | Sleep mode application: example                   | 42 |

|----|--------|---------------------------------------------------|----|

| 6. | Inter  | rupt                                              | 43 |

| (  | 6.1 Ir | nterrupt Overview                                 | 43 |

| (  | 6.2 E  | xternal interrupt                                 | 44 |

|    | 6.2.1  | INT0/INT1 interrupt                               | 44 |

|    | 6.2.2  | GPIO interrupt                                    | 44 |

| (  | 6.3 Ir | nterrupt and sleep wake-up                        | 44 |

| (  | 6.4 Ir | nterrupt Register                                 | 45 |

|    | 6.4.1  | Interrupt Mask Register                           | 45 |

|    | 6.4.2  | Interrupt Priority Control register               | 49 |

|    | 6.4.3  | Interrupt flag register                           |    |

|    | 6.4.4  | Clear operation of interrupt flag                 |    |

|    | 6.4.5  | Special interrupt flag in debug mode              | 58 |

| 7. | I/O p  | ort                                               | 59 |

| -  | 7.1    | SPIO function                                     | 59 |

|    | 7.1.1  | PORTx data register Px                            |    |

|    | 7.1.2  | PORTx direction register PxTRIS                   | 59 |

|    | 7.1.3  | PORTx Open Drain control register PxOD            |    |

|    | 7.1.4  | PORTx pull-up resistor control register PxUP      |    |

|    | 7.1.5  | PORTx pull-down resistor control register PxRD    |    |

|    | 7.1.6  | PORTx Drive current control register PxDR         |    |

|    | 7.1.7  | PORTx Slope control register PxSR                 | 61 |

|    | 7.1.8  | PORTx data input selection register PxDS          | 61 |

| -  | 7.2 N  | Multiplexed function                              | 62 |

|    | 7.2.1  | Port Multiplexing Configuration Register Function | 62 |

|    | 7.2.2  | Port input function allocation register           | 65 |

|    | 7.2.3  | Port external interrupt control register.         | 67 |

|    | 7.2.4  | Reuse function application note                   | 67 |

| 8. | Wato   | ch Dog Timer                                      | 68 |

| 8  | 8.1 C  | Overview                                          | 68 |

| 8  | 8.2 F  | Related registers                                 | 68 |

|    | 8.2.1  | Watchdog control register WDCON                   | 68 |

|    | 8.2.2  | Watchdog overflow control register CKCON          | 69 |

| 8  | 8.3 T  | he WDT Interrupt                                  |    |

|    | 8.3.1  | Interrupt Mask interrupt EIE2                     | 70 |

|    | 8.3.2  | Interrupt priority control register EIP2          | 71 |

| 9. | Wind   | dow watchdog timer(WWDT)                          | 72 |

|    |        |                                                   |    |

|    |        | Overview                                          |    |

| ,  |        | Related Register                                  |    |

|    | 9.2.1  | WWDT control register WWCON0                      |    |

|    | 9.2.2  | WWDT control register WWCON1                      |    |

|    | 9.2.3  | WWDT Compare RegisterWWCMPD                       |    |

| ,  |        | WDT Interrupt and sleep mode wake-up              |    |

|    | 9.3.1  | Interrupt Priority control register EIP3          |    |

|    |        | function Description                              |    |

| 10 |        | er 0/1                                            |    |

| •  |        | Overview                                          |    |

| •  |        | Related Register                                  |    |

| _  | 10.2.1 | Timer0/1 Mode Register TMOD                       | 77 |

|    |        |                                                   |    |

| 10.2.2 Timer0/1 control register TCON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 10.2.3 Timer0 Data Register Low bit TL0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 78  |

| 10.2.4 Timer0 Data Register high bit TH0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 78  |

| 10.2.5 Timer1 Data Register low bit TL1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 78  |

| 10.2.6 Timer1 Data Register high bit TH1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 79  |

| 10.2.7 Function Clock control register CKCON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 79  |

| 10.3 Timer0/1 Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 80  |

| 10.3.1 Interrupt mask register IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 80  |

| 10.3.2 Interrupt Priority control register IP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 81  |

| 10.3.3 Timer0/1、INT0/1 Interrupt flag registerTCON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 82  |

| 10.4 Timer0 working mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

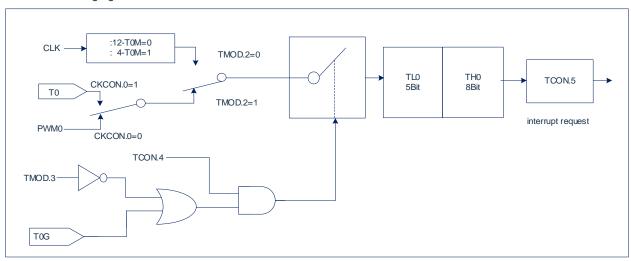

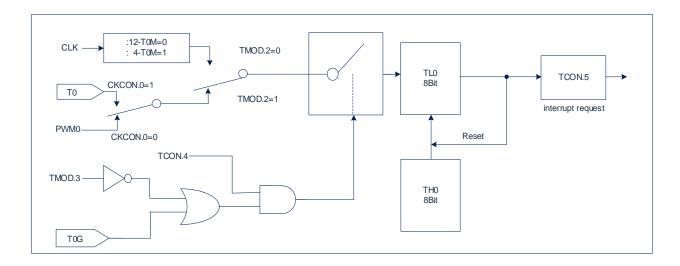

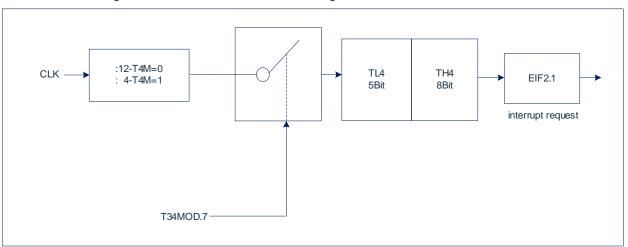

| 10.4.1 T0-Mode 0 (13-bit timer/counting mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 83  |

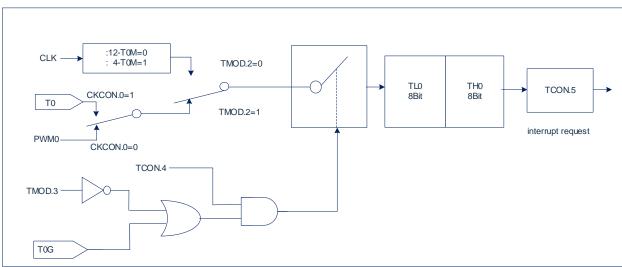

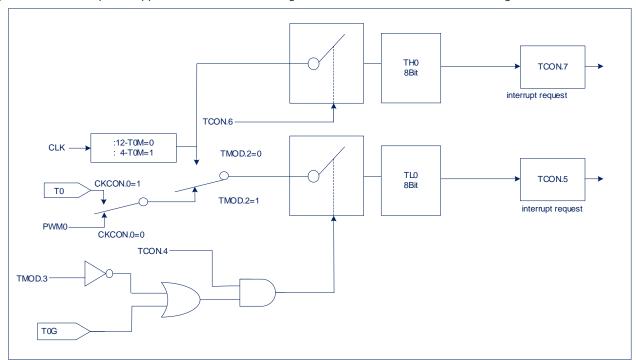

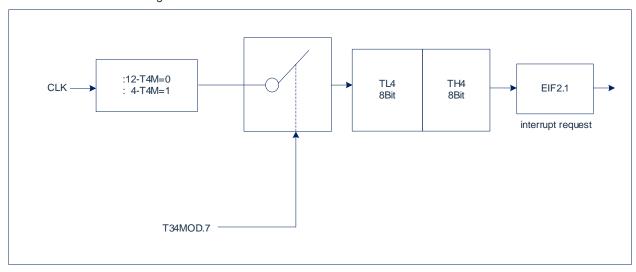

| 10.4.2 T0-Mode 1 (16-bit timer/counting mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

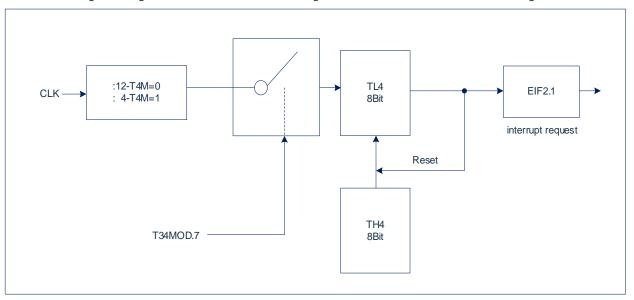

| 10.4.3 T0 - Mode 2 (8-bit auto reload timer / counter mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 84  |

| 10.4.4 T0-Mode 3 (two independent 8-bit timers/counters)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

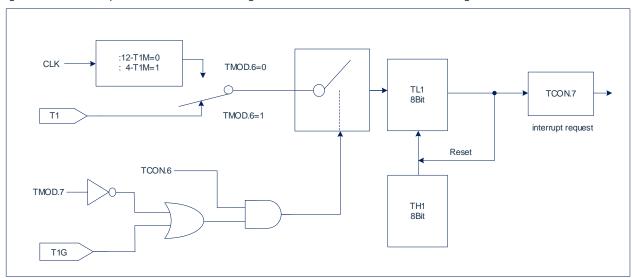

| 10.5 Timer1 working mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

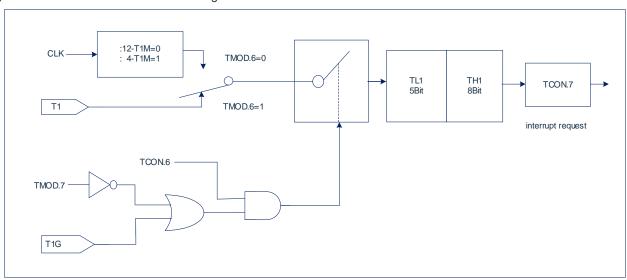

| 10.5.1 T1-Mode 0 (13-bit timer/counting mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 85  |

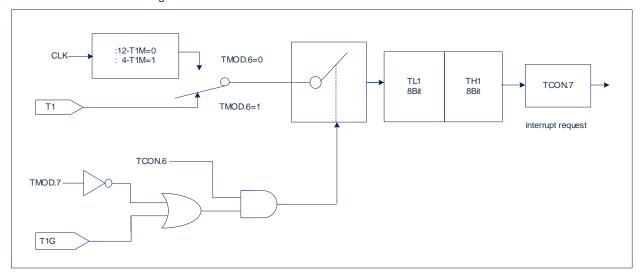

| 10.5.2 T1-Mode 1 (16-bit timer/counting mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 85  |

| 10.5.3 T1-Mode 2 (8-bit auto-reload timer/counting mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 86  |

| 10.5.4 T1-Mode 3 (stop counting)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 86  |

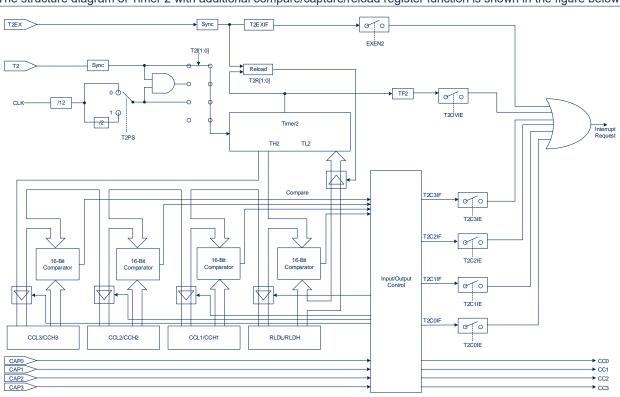

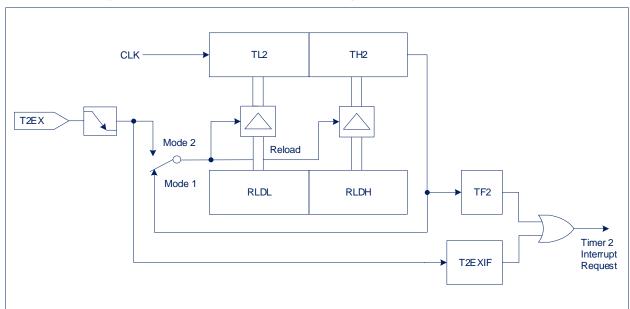

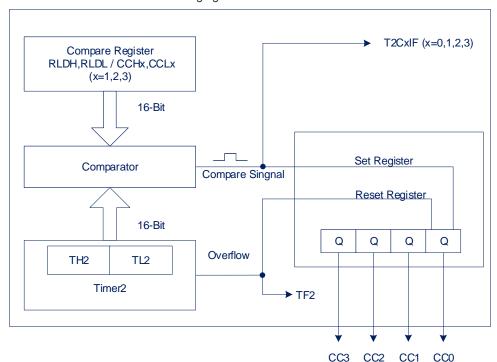

| 11. Timer2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 87  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| 11.2 Related Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| 11.2.2 Timer2 Data Register low bit TL2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| 11.2.3 Timer2 Data Register High bit TH2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| 11.2.4 Timer2 compare/capture/auto-reload register low bit RLI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

| 11.2.5 Timer2 compare/capture/auto-reload register low bit RL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| 11.2.6 Timer2 compare/capture channel1 Register low bit CCL <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| 11.2.7 Timer2 compare/capture channel1Register High bit CCF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| 11.2.8 Timer2 compare/capture channel2 Register low bitCCL2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| 11.2.9 Timer2 compare/capture channel2 Register high bit CCF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| 11.2.10 Timer2 compare/capture channel3 Register low bitCCL3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |